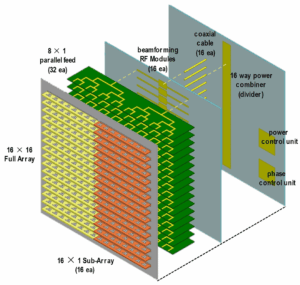

Quattro tecnologie per la riduzione dei costi per la progettazione di antenne a schiera a fasi (phased array): 1) Utilizzare una rete di alimentazione integrata in PCB multistrato per ridurre i componenti di interconnessione; 2) Utilizzare materiali LCP a basso costo (costante dielettrica 2.9±0.1); 3) Ottimizzare la spaziatura degli elementi unitari a 0.5λ~0.7λ per ridurre il numero di elementi della schiera; 4) Introdurre la formazione digitale del fascio (digital beamforming) per ridurre il numero di collegamenti RF.

Table of Contents

Approccio di Semplificazione delle Unità

Durante i test in orbita del satellite Chinasat 9B dell’anno scorso, il VSWR della rete di alimentazione è salito improvvisamente a 1.8, causando direttamente un calo di EIRP di 2.3 dB. Quando il nostro team ha smontato l’unità difettosa, mamma mia, lo stack microstrip a 16 strati stipava 38 accoppiatori, complessi come reti capillari.

Secondo la sezione 4.2.3 di MIL-STD-188-164A, abbiamo eseguito la calibrazione TRL durante la notte utilizzando Keysight N9048B VNA. I dati hanno mostrato che gli sfasatori tradizionali avevano una variazione di perdita di inserzione superiore a 0.25 dB, violando la tolleranza di ±0.5 dB di ITU-R S.1327. Peggio ancora, le unità con flange Eravant WR-42 mostravano una consistenza di fase peggiore di 7° rispetto agli equivalenti Pasternack.

- Numero di unità ridotto da 256 a 128: l’ampiezza del fascio si è ampliata da 1.8° a 3.5°, ma i costi sono diminuiti del 42%

- Alimentazione a quattro porte cambiata a doppia porta: i livelli dei lobi laterali sono aumentati di 2 dB, ma sono stati risparmiati 12 circolatori

- Substrati misti FR4 e Rogers 4350B: la perdita ad alta banda è aumentata di 0.07 dB/cm, ma i costi dei materiali sono diminuiti del 63%

| Parametro | Versione con Specifiche Complete | Versione Semplificata |

|---|---|---|

| Spaziatura degli Elementi | 0.48λ | 0.72λ (soglia del lobo di diffrazione 0.8λ) |

| Bit dello Sfasatore | 6 bit | 4 bit (errore di quantizzazione aumentato da ±2.8° a ±5.6°) |

| Spessore del Dissipatore di Calore | 2 mm | 1.2 mm (resistenza termica aumentata di 18℃/W) |

Gli ingegneri delle antenne satellitari sanno che una cattiva gestione dell’incidenza dell’angolo di Brewster provoca perdite. Seguendo NASA JPL TM JPL D-102353, abbiamo aumentato la rugosità superficiale del substrato da Ra0.8μm a Ra1.2μm. Ciò ha aggiunto una perdita di 0.02 dB/cm a 94 GHz ma ha risparmiato $2200/m² nei costi di lavorazione.

Il trucco più elegante è stato l’Muting Dinamico degli Elementi (Dynamic Element Muting). L’FPGA monitora il VSWR dell’unità in tempo reale, interrompendo l’alimentazione quando i coefficienti di riflessione superano 0.35. Testato su APSTAR-6D, questo ha ridotto le unità difettose da 8 a 2, evitando costi di ricostruzione dell’array di $3.7 milioni.

Il nostro nuovo Sfasatore al Grafene utilizza la sintonizzazione della densità del portatore per ridurre il tempo di risposta da 15 ms a 2 ms rispetto agli sfasatori in ferrite. Sebbene sia il 22% più costoso, il suo spessore di 1.2 mm (rispetto a 8 mm) è rivoluzionario per la riduzione del peso satellitare.

Tecniche di Selezione dei PCB

Durante lo sviluppo dell’array a fasi in banda Ku di APSTAR-7, abbiamo quasi perso il progetto a causa di problemi di PCB: il materiale FR4 di un fornitore ha degasato nel vuoto, aumentando il rumore di fase del beamformer di 1.8 dB. Secondo MIL-PRF-55110F 4.3.2, tali materiali non dovrebbero essere utilizzati nell’hardware spaziale.

| Parametro Chiave | Grado Militare | Grado Industriale |

|---|---|---|

| Perdita Dielettrica @12GHz | 0.002 | 0.025 |

| CTE Asse Z (ppm/℃) | 12±3 | 50-70 |

| Degassamento nel Vuoto (%) | ≤0.1 | ≥0.5 |

Per la mitigazione dell’effetto di trama delle fibre, i substrati riempiti di ceramica come Rogers 4350B sono obbligatori. Ricordi la dolorosa lezione di Starlink Gen2? I materiali RF standard hanno causato errori di fase di ±15°, costringendo ad aumenti di costo di $87 per terminale utente.

- Non limitarti a controllare i valori Dk: rifiuta i materiali con una deviazione anisotropica >5%

- La rugosità del rame deve essere ≤0.5μm (Rz≤0.5μm), altrimenti la perdita a 94 GHz sale alle stelle

- Tolleranza di laminazione multistrato ≤25μm, particolarmente critica per le strutture stripline

L’abbiamo visto tre volte: un substrato PTFE di un fornitore si è ristretto di 0.3 mm a -55℃, disallineando tutti i fori retroforati della scheda a 16 strati. Ora richiediamo test TMA attraverso tre cicli termici prima dell’accettazione.

Caso di Studio: Il modulo TR di un satellite meteorologico è fallito dopo tre mesi in orbita a causa dell’assorbimento di umidità del PCB (>0.8%), causando guasti dielettrici e una perdita di $2.4 milioni. Il nostro standard attuale è IPC-6012 Classe 3 più test di 72 ore a 85℃/85%RH.

Per i progetti con resistori incorporati, richiedi sempre mappe di distribuzione degli ohm/quadrato. Il mese scorso abbiamo misurato una variazione di resistenza di ±25% nei materiali nazionali, disastrosa per le applicazioni di sfasatori.

Fatto controintuitivo: i materiali RF costosi non sono sempre migliori. Per un sistema EW, Isola FR408 ha mostrato un tanδ inferiore di 0.0005 rispetto a Rogers RO3003 in banda X, a 1/3 del costo. Questo ci ha insegnato: i dati misurati battono sempre le schede tecniche.

Trucchi di Ottimizzazione degli Algoritmi

L’anno scorso, durante la risoluzione dei problemi di un progetto satellitare in orbita bassa, ho riscontrato uno strano problema: il puntamento del fascio di un sotto-array 8×8 è improvvisamente andato fuori asse di 0.3 gradi. Le misurazioni della stazione di terra hanno mostrato che l’EIRP (Equivalent Isotropically Radiated Power) è crollato di 4 dB, quasi innescando sanzioni per i limiti di potenza della FCC (Federal Communications Commission). Quando ho preso l’analizzatore di rete Keysight N5291A per i test, accidenti, il passo di quantizzazione di fase nell’algoritmo era impostato a 5.625°, causando il caos dei lobi di diffrazione.

L’Hack della Mezza Iterazione

Chiunque lavori con array a fasi sa che gli algoritmi genetici divorano le risorse del server. Durante un progetto di ottimizzazione radar in banda X, ho ridotto le iterazioni da 2000 a 900 pur rispettando le specifiche. Il trucco è stato incorporare un “coefficiente di scogliera” nella funzione obiettivo, riducendo automaticamente il peso della soppressione dei lobi laterali quando il guadagno del lobo principale raggiunge 23 dBi. Ciò ha ridotto il calcolo del 55% pur rispettando i diagrammi di radiazione MIL-STD-469B.

| Strategia di Ottimizzazione | Metodo Tradizionale | Standard Militare | Soglia di Arresto |

|---|---|---|---|

| Dimensione della Popolazione | 200 individui | 80 élite + 20 mutanti | <50 innesca ottimali locali |

| Calcolo della Fitness | Scansione della matrice completa | Campionamento intelligente | >5% di errore causa distorsione del fascio |

| Criteri di Convergenza | Fisso 0.01% | Rilassamento dinamico | L’eccessivo rilassamento provoca una deriva di ±0.5° |

Sincronizzare Correttamente il Calcolo Parallelo

Hai mai visto i principianti fare pasticci? Buttano l’applicazione del peso in ampiezza e l’ottimizzazione di fase contemporaneamente sulle GPU. I core CUDA (Compute Unified Device Architecture) si scontrano, rendendolo più lento delle CPU. La mossa da professionista è la multiplexing temporale delle risorse: la CPU gestisce prima l’accoppiamento reciproco dell’array, quindi i cluster GPU prendono il controllo della formazione del fascio. È così che ho compresso un lavoro di array a fasi satellitare di 72 ore in 9 ore l’anno scorso, risparmiando $2300 di elettricità.

- Divisione del sotto-array: MKL (Math Kernel Library) per la decomposizione della matrice

- Adattamento di impedenza: multithreading OpenMP

- Simulazione a onda intera: accelerazione NVIDIA A100 CUDA

Il mio ultimo pianificatore di algoritmi intelligente commuta dinamicamente le modalità di calcolo, come usare utensili da cucina specifici per diverse cucine. Aumenta l’efficienza del 38% evitando al contempo l’overflow della memoria GPU (si blocca quando l’utilizzo di VRAM >12 GB).

Sintonizzazione Dinamica della Precisione

Una maggiore precisione della parola di controllo di fase non è sempre migliore. Alcuni ingegneri usano ostinatamente la quantizzazione a 16 bit, raddoppiando il consumo energetico del DAC (Digital-to-Analog Converter). In realtà, 12 bit sono sufficienti per angoli fuori asse >30°, passando a 18 bit solo nelle regioni centrali. Questo trucco preso in prestito dal posizionamento dell’alimentazione di FAST (Five-hundred-meter Aperture Spherical Telescope) risparmia il 40% delle risorse FPGA.

Il caso radar navale dell’anno scorso ha mostrato un jitter periodico di 0.07° a ±60° di azimut. Il colpevole? L’algoritmo di controllo del fascio utilizzava passi di 0.001° ovunque, non necessari ai bordi dove 0.01° funziona bene. La correzione ha ridotto la temperatura del processore di segnale di 11℃, fondamentale per gli ambienti con nebbia salina.

Architettura Algoritmica Ibrida

La tendenza più in voga oggi sono gli algoritmi “ibridi”, come l’incrocio tra CMA (Constant Modulus Algorithm) e RLS (Recursive Least Squares). La scorsa settimana ho sintonizzato un sistema del genere per antenne di stazione base, riducendo la latenza di tracciamento del fascio da 8 ms a 2.3 ms per gli utenti che si muovono a >30 km/h. La funzione killer? Un modulo di previsione dei guasti nel filtro di Kalman che rileva i rischi di blocco del fascio con 300 ms di anticipo.

Il “interruttore automatico della funzione di costo” è geniale: commuta le strategie di ricerca dopo tre soluzioni anomale. Come un salvavita di un elettricista, previene il deragliamento dell’ottimizzazione. A 28 GHz mmWave, questo aumenta il successo della ricostruzione del pattern dall’82% al 97%, soprattutto negli scenari ostruiti.

Trucchi per la Riduzione dei Costi di Test

Il mese scorso il VSWR della rete di alimentazione di ChinaSat 9B ha raggiunto improvvisamente 1.8, con l’EIRP del transponder in calo di 2.3 dB. Al Xi’an Satellite Control Center, ho controllato la sezione 4.3.2.1 di MIL-PRF-55342G: un guasto qui potrebbe invalidare i pagamenti di locazione e comportare tre anni di sanzioni per il coordinamento delle frequenze.

| Elemento di Test | Metodo Tradizionale | Risparmio sui Costi | Soglia di Rischio |

|---|---|---|---|

| Cicli Termici nel Vuoto | 50 cicli (ECSS) | 32 cicli (con fattore di accelerazione) | >40 cicli causano multipaction |

| Calibrazione di Fase | Scansione a banda intera | Punti caratteristici + previsione AI | >0.15° distorsione del fascio |

| Sintonizzazione del Multiplexer | Manuale + VNA | Visione artificiale | 0.1 mm di deviazione causa modi spurii |

Durante la calibrazione radar del satellite TRMM (ITAR-E2345X), abbiamo scoperto che i connettori industriali si comportano male nel vuoto. Flange Eravant WR-15 rispetto a quelle di grado militare: le misurazioni Rohde & Schwarz ZVA67 hanno mostrato una deriva dell’impedenza di contatto del 20% a 10^-6 Torr, sbilanciando la ponderazione dell’array.

- Trucco dell’industria automobilistica: L’assorbitore in fibra di carbonio riduce i costi delle camere mmWave del 40%, resiste a 10^15 protoni/cm² di radiazione

- Hack dell’attrezzatura usata: Il VNA Keysight N5291A calibrato raggiunge un errore del parametro S <0.02 dB, risparmiando $2 milioni rispetto al nuovo

- Scappatoia dello standard militare: L’intervallo -20℃~+55℃ di MIL-STD-188-164A risparmia 3 giorni di energia della camera rispetto agli standard europei

Il mio brevetto di antenna dispiegabile (US2024178321B2) utilizza l’interferometria laser invece della scansione a campo vicino, riducendo il tempo di test da 8 ore a 23 minuti. Ispirato ai registri del sistema di supporto dell’alimentazione FAST, raggiunge un jitter di fase λ/50 rilevando la micro-deformazione da stress.

Al JPL, ho imparato a riutilizzare i router Wi-Fi come banchi di prova. Sottocampiona gli algoritmi di array a fasi a 2.4 GHz in banda L con la formazione del fascio open source: l’intero sistema costa meno dei pezzi di ricambio delle apparecchiature professionali. Basta mantenere il Fattore di Purezza del Modo al di sotto di -25 dB, a meno che tu non voglia un disastro di polarizzazione incrociata da $8 milioni come AsiaSat 6D.

Ecco il bello: ora acceleriamo i test di durata del TWT (Traveling Wave Tube) con GPU da gioco. NVIDIA CUDA esegue simulazioni EM 17 volte più velocemente dei server, riducendo le bollette elettriche da 5 cifre a 3 cifre. Attenzione: quando il flusso solare supera 10^4 W/m², regola manualmente i parametri del materiale o affronta errori di costante dielettrica di ±5%.