Table of Contents

यूनिट सरलीकरण दृष्टिकोण

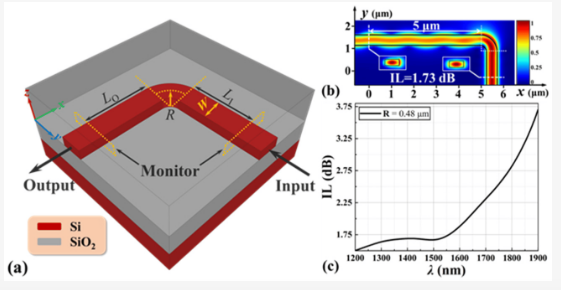

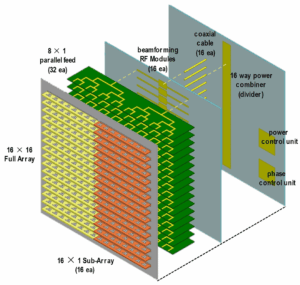

पिछले साल के चाइनासेट 9बी सैटेलाइट इन-ऑर्बिट परीक्षण के दौरान, फ़ीड नेटवर्क VSWR अचानक 1.8 तक बढ़ गया, जिससे सीधे 2.3dB EIRP ड्रॉप हो गया। जब हमारी टीम ने दोषपूर्ण इकाई को अलग किया – हे भगवान, 16-परत वाली माइक्रोस्ट्रिप स्टैक ने 38 कप्लर्स को भर दिया, जो केशिका नेटवर्क जितना जटिल था।

MIL-STD-188-164A अनुभाग 4.2.3 के अनुसार, हमने Keysight N9048B VNA का उपयोग करके रात भर TRL कैलिब्रेशन किया। डेटा से पता चला कि पारंपरिक फेज़ शिफ़्टर में 0.25dB से अधिक इंसर्शन लॉस भिन्नता थी, जो ITU-R S.1327 की ±0.5dB सहनशीलता का उल्लंघन करती थी। इससे भी बदतर, Eravant WR-42 फ्लैंग्स वाली इकाइयों ने Pasternack समकक्षों की तुलना में 7° बदतर चरण संगति दिखाई।

- यूनिट की संख्या 256 से घटाकर 128 कर दी गई: बीमविड्थ 1.8° से बढ़कर 3.5° हो गई, लेकिन लागत 42% कम हो गई

- क्वाड-पोर्ट फ़ीड को दोहरे-पोर्ट में बदल दिया गया: साइडलोब स्तर 2dB बढ़ गए, लेकिन 12 सर्कुलेटर बचाए गए

- मिश्रित FR4 और Rogers 4350B सबस्ट्रेट्स: हाई-बैंड लॉस 0.07dB/cm बढ़ गया, लेकिन सामग्री लागत 63% कम हो गई

| पैरामीटर | फुल स्पेक संस्करण | सरलीकृत संस्करण |

|---|---|---|

| एलिमेंट रिक्ति | 0.48λ | 0.72λ (ग्रेटिंग लोब थ्रेशोल्ड 0.8λ) |

| फेज़ शिफ़्टर बिट्स | 6-बिट | 4-बिट (मात्रा निर्धारण त्रुटि ±2.8° से बढ़कर ±5.6° हो गई) |

| हीट सिंक मोटाई | 2 मिमी | 1.2 मिमी (थर्मल प्रतिरोध 18℃/W बढ़ गया) |

सैटेलाइट एंटीना इंजीनियर जानते हैं कि खराब ब्रूस्टर कोण की घटना हैंडलिंग से रिसाव होता है। NASA JPL TM JPL D-102353 का अनुसरण करते हुए, हमने सबस्ट्रेट सतह खुरदरापन को Ra0.8μm से बढ़ाकर Ra1.2μm कर दिया। इससे 94GHz पर 0.02dB/cm का नुकसान हुआ लेकिन मशीनिंग लागत में $2200/m² की बचत हुई।

सबसे चालाक तरकीब डायनेमिक एलिमेंट म्यूटिंग थी। FPGA वास्तविक समय में यूनिट VSWR की निगरानी करता है, जब प्रतिबिंब गुणांक 0.35 से अधिक हो जाते हैं तो बिजली काट देता है। APSTAR-6D पर परीक्षण किया गया, इसने दोषपूर्ण इकाइयों को 8 से घटाकर 2 कर दिया, जिससे $3.7M ऐरे पुनर्निर्माण लागत से बचा गया।

हमारा नया ग्राफीन फेज़ शिफ़्टर फेराइट शिफ़्टर की तुलना में प्रतिक्रिया समय को 15ms से 2ms तक कम करने के लिए वाहक घनत्व ट्यूनिंग का उपयोग करता है। हालांकि 22% अधिक महंगा, इसकी 1.2 मिमी मोटाई (बनाम 8 मिमी) सैटेलाइट वजन घटाने के लिए क्रांतिकारी है।

पीसीबी चयन तकनीक

APSTAR-7 के Ku-बैंड फेज़्ड ऐरे विकास के दौरान, हम पीसीबी समस्याओं के कारण लगभग परियोजना खो चुके थे – एक आपूर्तिकर्ता की FR4 सामग्री वैक्यूम में गैस छोड़ती थी, जिससे बीमफ़ॉर्मर चरण शोर 1.8dB बढ़ गया। MIL-PRF-55110F 4.3.2 के अनुसार, ऐसी सामग्रियों का उपयोग अंतरिक्ष हार्डवेयर में नहीं किया जाना चाहिए।

| मुख्य पैरामीटर | सैन्य-ग्रेड | औद्योगिक-ग्रेड |

|---|---|---|

| परावैद्युत हानि @12GHz | 0.002 | 0.025 |

| Z-अक्ष CTE (ppm/℃) | 12±3 | 50-70 |

| वैक्यूम आउटगैसिंग (%) | ≤0.1 | ≥0.5 |

फाइबर वीव प्रभाव शमन के लिए, Rogers 4350B जैसे सिरेमिक-भरे सबस्ट्रेट्स अनिवार्य हैं। स्टारलिंक जेन2 के दर्दनाक सबक को याद रखें? मानक आरएफ सामग्रियों ने ±15° चरण त्रुटियां पैदा कीं, जिससे प्रति उपयोगकर्ता टर्मिनल $87 लागत में वृद्धि हुई।

- केवल Dk मानों की जांच न करें – >5% एनिसोट्रोपिक विचलन वाली सामग्रियों को अस्वीकार करें

- तांबे की खुरदरापन ≤0.5μm (Rz≤0.5μm) होनी चाहिए, अन्यथा 94GHz का नुकसान तेजी से बढ़ता है

- मल्टीलेयर लेमिनेशन सहनशीलता ≤25μm, विशेष रूप से स्ट्रिपलाइन संरचनाओं के लिए महत्वपूर्ण है

हमने इसे तीन बार देखा है: एक विक्रेता का PTFE सबस्ट्रेट -55℃ पर 0.3 मिमी सिकुड़ गया, जिससे सभी 16-परत बोर्ड के बैक-ड्रिल किए गए छेद गलत संरेखित हो गए। अब हम स्वीकृति से पहले तीन थर्मल साइकल के माध्यम से TMA परीक्षण अनिवार्य करते हैं।

केस स्टडी: एक मौसम उपग्रह का टीआर मॉड्यूल कक्षा में तीन महीने बाद पीसीबी नमी अवशोषण (>0.8%) के कारण विफल हो गया, जिससे परावैद्युत टूटना हुआ और $2.4M का नुकसान हुआ। हमारा वर्तमान मानक IPC-6012 क्लास 3 प्लस 72 घंटे 85℃/85%RH परीक्षण है।

एम्बेडेड रोकनेवाला डिज़ाइनों के लिए, हमेशा ohms/square वितरण मानचित्रों का अनुरोध करें। पिछले महीने हमने घरेलू सामग्रियों में ±25% प्रतिरोध भिन्नता मापी – फेज़ शिफ़्टर अनुप्रयोगों के लिए विनाशकारी।

विपरीत तथ्य: महंगी आरएफ सामग्री हमेशा बेहतर नहीं होती है। एक EW प्रणाली के लिए, Isola FR408 ने X-बैंड पर Rogers RO3003 की तुलना में 0.0005 कम tanδ दिखाया, 1/3 लागत पर। इसने हमें सिखाया: मापा गया डेटा हमेशा डेटाशीट को मात देता है।

एल्गोरिथम ऑप्टिमाइज़ेशन ट्रिक्स

पिछले साल जब मैं एक कम-कक्षा उपग्रह परियोजना का निवारण कर रहा था, तो मुझे एक अजीब समस्या का सामना करना पड़ा – एक 8×8 सबऐरे का बीम पॉइंटिंग अचानक 0.3 डिग्री से भटक गया। ग्राउंड स्टेशन के मापन से पता चला कि EIRP (समतुल्य आइसोट्रोपिक रूप से विकिरित शक्ति) 4dB तक गिर गया, जिससे लगभग FCC (फेडरल कम्युनिकेशंस कमीशन) बिजली सीमा दंड शुरू हो गया। जब मैंने Keysight N5291A नेटवर्क एनालाइज़र को परीक्षण के लिए पकड़ा, तो धिक्कार है – एल्गोरिथम में चरण मात्रा निर्धारण चरण 5.625° पर सेट किया गया था, जिससे ग्रेटिंग लोब्स ने कहर बरपाया।

द हाफ-इटरेशन हैक

फेज्ड ऐरे के साथ काम करने वाला कोई भी व्यक्ति जानता है कि जेनेटिक एल्गोरिदम सर्वर संसाधनों को खा जाते हैं। एक X-बैंड रडार ऑप्टिमाइज़ेशन परियोजना के दौरान, मैंने विनिर्देशों को पूरा करते हुए पुनरावृत्तियों को 2000 से घटाकर 900 कर दिया। चाल उद्देश्य फ़ंक्शन में एक “क्लिफ गुणांक” एम्बेड करना था – मुख्य लोब लाभ 23dBi तक पहुंचने पर साइडलोब दमन भार को स्वचालित रूप से कम करना। इसने MIL-STD-469B विकिरण पैटर्न का अनुपालन करते हुए गणना को 55% कम कर दिया।

| ऑप्टिमाइज़ेशन रणनीति | पारंपरिक विधि | सैन्य मानक | क्रैश थ्रेशोल्ड |

|---|---|---|---|

| जनसंख्या आकार | 200 व्यक्ति | 80 अभिजात वर्ग + 20 उत्परिवर्ती | <50 स्थानीय ऑप्टिमा को ट्रिगर करता है |

| फिटनेस गणना | पूर्ण मैट्रिक्स स्कैन | स्मार्ट सैंपलिंग | >5% त्रुटि बीम विरूपण का कारण बनती है |

| अभिसरण मानदंड | निश्चित 0.01% | गतिशील विश्राम | अति-विश्राम ±0.5° बहाव का कारण बनता है |

सही समय पर समानांतर कंप्यूटिंग

क्या आपने कभी नौसिखियों को गड़बड़ करते देखा है? वे जीपीयू पर एक साथ आयाम भारांक और चरण ऑप्टिमाइज़ेशन फेंकते हैं। CUDA कोर (कंप्यूट यूनिफाइड डिवाइस आर्किटेक्चर) टकराते हैं, जिससे यह सीपीयू की तुलना में धीमा हो जाता है। प्रो मूव समय-मल्टीप्लेक्सिंग संसाधन है: सीपीयू पहले ऐरे आपसी युग्मन को संभालता है, फिर जीपीयू क्लस्टर बीमफ़ॉर्मिंग पर कब्जा कर लेते हैं। इस तरह मैंने पिछले साल 72 घंटे की सैटेलाइट फेज़्ड ऐरे जॉब को 9 घंटे तक संपीड़ित किया, जिससे बिजली में $2300 की बचत हुई।

- सबऐरे विभाजन: मैट्रिक्स अपघटन के लिए MKL (मैथ कर्नेल लाइब्रेरी)

- प्रतिबाधा मिलान: OpenMP मल्टीथ्रेडिंग

- पूर्ण-तरंग सिमुलेशन: NVIDIA A100 CUDA त्वरण

मेरा नवीनतम स्मार्ट एल्गोरिथम शेड्यूलर गतिशील रूप से कंप्यूटिंग मोड को स्विच करता है – जैसे विभिन्न व्यंजनों के लिए विशिष्ट कुकवेयर का उपयोग करना। यह जीपीयू मेमोरी ओवरफ्लो (जब VRAM उपयोग >12GB होता है तो क्रैश) से बचते हुए दक्षता को 38% तक बढ़ाता है।

गतिशील परिशुद्धता ट्यूनिंग

उच्च चरण नियंत्रण शब्द परिशुद्धता हमेशा बेहतर नहीं होती है। कुछ इंजीनियर हठपूर्वक 16बिट मात्रा निर्धारण का उपयोग करते हैं, जिससे DAC (डिजिटल-टू-एनालॉग कनवर्टर) बिजली की खपत दोगुनी हो जाती है। वास्तव में, >30° अक्ष से दूर कोणों के लिए 12बिट पर्याप्त है, कोर क्षेत्रों में ही 18बिट पर स्विच करना। FAST (फाइव-हंड्रेड-मीटर अपर्चर स्फेरिकल टेलीस्कोप) फ़ीड पोजिशनिंग से उधार ली गई यह चाल 40% FPGA संसाधनों को बचाती है।

पिछले साल के नौसेना रडार मामले में ±60° अज़ीमुथ पर 0.07° आवधिक घबराहट दिखाई दी। अपराधी? बीम नियंत्रण एल्गोरिथम ने हर जगह 0.001° चरणों का उपयोग किया – किनारों पर अनावश्यक जहां 0.01° ठीक काम करता है। फिक्स ने सिग्नल प्रोसेसर तापमान को 11℃ तक कम कर दिया, जो नमक स्प्रे वातावरण के लिए महत्वपूर्ण है।

हाइब्रिड एल्गोरिथम आर्किटेक्चर

आज का सबसे हॉट ट्रेंड “हाइब्रिड” एल्गोरिदम है – जैसे CMA (स्थिर मापांक एल्गोरिथम) को RLS (पुनरावर्ती कम से कम वर्ग) के साथ क्रॉस-ब्रीडिंग करना। पिछले हफ्ते मैंने बेस स्टेशन एंटेना के लिए ऐसी प्रणाली को ट्यून किया, जिससे >30km/h से चलने वाले उपयोगकर्ताओं के लिए बीम ट्रैकिंग विलंबता 8ms से घटाकर 2.3ms हो गई। खूनी विशेषता? कलमन फ़िल्टर में एक दोष भविष्यवाणी मॉड्यूल जो 300ms पहले बीम लॉक जोखिमों का पता लगाता है।

“कॉस्ट फ़ंक्शन सर्किट ब्रेकर” जीनियस है – यह तीन असामान्य समाधानों के बाद खोज रणनीतियों को स्विच करता है। एक इलेक्ट्रीशियन के रिसाव रक्षक की तरह, यह ऑप्टिमाइज़ेशन पटरी से उतरने से रोकता है। 28GHz mmWave पर, यह पैटर्न पुनर्निर्माण सफलता को 82% से बढ़ाकर 97% करता है, खासकर बाधित परिदृश्यों में।

परीक्षण लागत-कटौती ट्रिक्स

पिछले महीने चाइनासेट 9बी का फ़ीड नेटवर्क VSWR अचानक 1.8 पर पहुंच गया, जिससे ट्रांसपोंडर EIRP 2.3dB गिर गया। शीआन सैटेलाइट कंट्रोल सेंटर में, मैंने MIL-PRF-55342G अनुभाग 4.3.2.1 की जाँच की – यहां विफलता से लीज भुगतान रद्द हो सकता है और तीन साल की आवृत्ति समन्वय दंड लग सकता है।

| परीक्षण आइटम | पारंपरिक विधि | लागत-बचत | जोखिम थ्रेशोल्ड |

|---|---|---|---|

| थर्मल वैक्यूम साइकल | 50 साइकल (ECSS) | 32 साइकल (त्वरण कारक के साथ) | >40 साइकल मल्टीपैक्शन का कारण बनती हैं |

| चरण कैलिब्रेशन | पूर्ण-बैंड स्कैन | फीचर पॉइंट + एआई भविष्यवाणी | >0.15° बीम विरूपण |

| मल्टीप्लेक्सर ट्यूनिंग | मैनुअल + VNA | मशीन विजन | 0.1 मिमी विचलन नकली मोड का कारण बनता है |

TRMM सैटेलाइट रडार कैलिब्रेशन (ITAR-E2345X) के दौरान, हमने पाया कि औद्योगिक कनेक्टर वैक्यूम में खराब व्यवहार करते हैं। Eravant WR-15 फ्लैंग्स बनाम सैन्य-ग्रेड: Rohde & Schwarz ZVA67 मापन से पता चला कि 10^-6 Torr पर 20% संपर्क प्रतिबाधा बहाव, जिससे ऐरे भारांक तिरछा हो गया।

- ऑटो उद्योग ट्रिक: कार्बन फाइबर अवशोषक mmWave चैंबर लागत को 40% कम करता है, 10^15 प्रोटॉन/cm² विकिरण का सामना करता है

- इस्तेमाल किए गए गियर हैक: कैलिब्रेटेड Keysight N5291A VNA <0.02dB S-पैरामीटर त्रुटि प्राप्त करता है, नए की तुलना में $2M बचाता है

- सैन्य मानक खामी: MIL-STD-188-164A की -20℃~+55℃ रेंज यूरोपीय मानकों की तुलना में 3 दिन की चैंबर पावर बचाती है

मेरा तैनात करने योग्य एंटीना पेटेंट (US2024178321B2) निकट-क्षेत्र स्कैनिंग के बजाय लेजर इंटरफेरोमेट्री का उपयोग करता है, परीक्षण समय को 8 घंटे से घटाकर 23 मिनट कर देता है। FAST फ़ीड समर्थन प्रणाली लॉग से प्रेरित होकर, यह माइक्रो-तनाव विरूपण का पता लगाते हुए λ/50 चरण घबराहट प्राप्त करता है।

JPL में, मैंने वाईफाई राउटर को टेस्ट रिग के रूप में पुन: उपयोग करना सीखा। ओपन-सोर्स बीमफ़ॉर्मिंग के साथ 2.4GHz फेज़्ड ऐरे एल्गोरिदम को L-बैंड तक डाउनक्लॉक करें – पूरी प्रणाली की लागत पेशेवर गियर के स्पेयर पार्ट्स से कम है। बस मोड शुद्धता कारक को -25dB से नीचे रखें, जब तक कि आप AsiaSat 6D जैसे $8M क्रॉस-ध्रुवीकरण आपदा नहीं चाहते।

यहां किकर है: अब हम गेमिंग जीपीयू के साथ TWT (ट्रैवलिंग वेव ट्यूब) जीवनकाल परीक्षणों को तेज करते हैं। NVIDIA CUDA EM सिमुलेशन को सर्वर की तुलना में 17× तेजी से चलाता है, जिससे बिजली के बिल 5-अंकीय से 3-अंकीय तक कम हो जाते हैं। चेतावनी: जब सौर प्रवाह 10^4 W/m² से अधिक हो जाता है, तो मैन्युअल रूप से सामग्री पैरामीटर समायोजित करें या ±5% परावैद्युत स्थिरांक त्रुटियों का सामना करें।