표면 저항을 60% 줄이기 위해 밀리미터파 대역에서 금 도금(두께 3-5 $\mu m$)을 적용합니다. 누설을 방지하기 위해 정밀한 플랜지 정렬($\le 25 \mu m$ 오프셋)을 구현하고, 습도로 인한 유전체 손실을 제거하기 위해 건조 공기 가압(0.5-1 bar)을 배치합니다.

Table of Contents

저손실 재료 선택

도파관 손실은 광학 및 RF 시스템에서 신호 무결성과 전력 효율에 직접적인 영향을 미치는 중요한 요소입니다. 예를 들어, 실리콘 포토닉스에서 일반적인 전파 손실은 재료 흡수 및 산란으로 인해 2-5 dB/cm 범위입니다. 올바른 재료를 선택하면 손실을 30-70% 줄여 시스템 성능을 크게 향상시킬 수 있습니다. 예를 들어, 질화규소($Si_3N_4$) 도파관은 실리콘의 1-3 dB/cm에 비해 0.1 dB/cm만큼 낮은 손실을 나타내어 저전력 응용 분야에 이상적입니다. 마찬가지로, RF 도파관에서 알루미늄(Al)은 표면 저항이 $2.65 \mu\Omega \cdot cm$인 반면, 은(Ag)은 이를 $1.59 \mu\Omega \cdot cm$로 줄여 도체 손실을 40% 낮춥니다.

코어와 클래딩 재료 사이의 굴절률 대비 또한 핵심적인 역할을 합니다. 실리콘($n \approx 3.5$)과 같은 고굴절률 재료는 강력한 빛 가둠을 가능하게 하지만 더 높은 산란 손실을 겪습니다. 이와 대조적으로, 실리카($SiO_2$, $n \approx 1.45$)는 초저손실(섬유에서 0.03 dB/km)을 제공하지만 더 큰 도파관 치수를 필요로 합니다. 균형 잡힌 접근 방식은 실리콘 온 인슐레이터(SOI)를 사용하는 것으로, 2 $\mu m$ 매립 산화물 위에 220 nm 실리콘 층이 있어 컴팩트한 모드 가둠으로 0.5-1 dB/cm 손실을 제공합니다.

RF 응용 분야의 경우, 구리 코팅 강철 도파관은 비용을 절감하는 동시에 순수 구리 전도도의 90%를 유지하여 맨 강철에 비해 손실을 15% 줄입니다. 고분자 도파관에서 PMMA(아크릴)는 850 nm에서 0.3-0.5 dB/cm 손실을 보이고, CYTOP과 같은 불소화 고분자는 0.1 dB/cm를 달성하여 단거리 광학 상호 연결에 적합합니다.

제작 불순물 또한 손실에 기여합니다. 실리카의 철(Fe) 1 ppm조차도 흡수를 0.1 dB/km 증가시킵니다. 고순도 반도체 등급 실리콘(99.9999%)은 흡수 관련 손실을 0.2 dB/cm 미만으로 줄입니다. RF 도파관의 경우, 5-10 $\mu m$ 은으로 전기도금하면 표면 평활도가 향상되어 맨 알루미늄에 비해 도체 손실이 20-30% 감소합니다.

도파관 설계 최적화

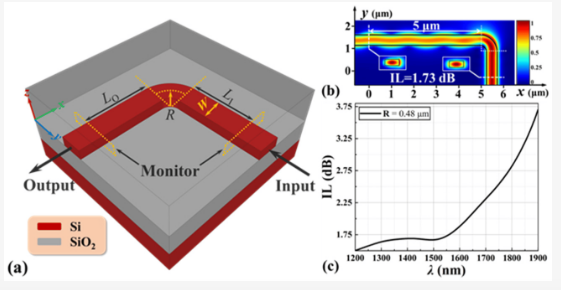

도파관 설계는 성능에 직접적인 영향을 미칩니다. 불량한 기하학적 구조는 손실을 200-300% 증가시킬 수 있는 반면, 최적화된 구조는 포토닉스에서 <0.1 dB/cm 및 RF 시스템에서 <0.01 dB/m를 달성합니다. 예를 들어, 500 nm $\times$ 220 nm 실리콘 도파관은 날카로운 90° 굽힘에서 3 dB/cm를 손실하지만, 600 nm $\times$ 250 nm로 넓히면 굽힘 손실이 0.5 dB/cm로 줄어듭니다. RF에서 0.1 mm 표면 거칠기를 가진 WR-90 도파관(10 GHz)은 0.02 dB/m 손실을 가지지만, 0.01 $\mu m$ 거칠기로 연마하면 손실이 40% 줄어듭니다.

모드 가둠은 매우 중요합니다. 15 $\mu m$ 클래딩을 가진 3 $\mu m$ 실리카 코어는 95% 빛 가둠을 보장하여 누설을 최소화합니다. 이를 1 $\mu m$ 코어와 비교해 보면, 모드의 30%가 클래딩으로 흘러나와 손실이 1.5 dB/cm 증가합니다. RF의 경우, 직사각형 도파관(예: 10 GHz의 경우 23 mm $\times$ 10 mm)은 낮은 모드 분산으로 인해 원형 도파관보다 전력 처리에서 15% 더 우수합니다.

굽힘 반경은 손실에 극적인 영향을 미칩니다. 실리콘 포토닉스에서 5 $\mu m$ 반경은 10 dB/cm 손실을 유발하는 반면, 이를 20 $\mu m$로 늘리면 손실이 0.2 dB/cm로 떨어집니다. 다음은 1550 nm 파장에 대한 굽힘 반경 대 손실 비교입니다.

| 굽힘 반경 ($\mu m$) | 손실 (dB/cm) |

|---|---|

| 5 | 10.0 |

| 10 | 2.5 |

| 20 | 0.2 |

| 50 | 0.05 |

테이퍼링된 전이는 삽입 손실을 줄입니다. 5 $\mu m$ 섬유와 500 nm 도파관 사이의 100 $\mu m$ 선형 테이퍼는 결합 손실을 3 dB에서 0.5 dB로 줄입니다. 유사하게, RF에서 3단계 임피던스 변환기는 20 GHz에서 불일치 손실을 1.2 dB에서 0.3 dB로 줄입니다.

슬롯 도파관(예: 150 nm 실리콘 슬롯)은 빛-물질 상호 작용을 향상시켜 기존 설계에 비해 센서 감도를 5배 높입니다. 그러나 50% 더 높은 산란 손실을 피하기 위해 <10 nm 제작 정밀도가 필요합니다.

재료 스택 또한 중요합니다. 실리콘 온 사파이어 도파관은 실리콘 온 인슐레이터(SOI)에 비해 기판 누설을 60% 줄이지만, 비용은 3배 더 비쌉니다. 저예산 프로젝트의 경우, 3 $\mu m$ 매립 산화물을 가진 SOI는 0.8 dB/cm의 절충안을 제공합니다.

제작 품질 향상

도파관 성능은 제작 품질에 달려 있습니다. 사소한 결함이라도 손실을 50-200% 급증시킬 수 있습니다. 예를 들어, 실리콘 포토닉스에서 1 nm 측벽 거칠기는 0.01 dB/cm 손실을 추가하지만, 5 nm 거칠기(기본 에칭에서 일반적)는 0.5 dB/cm로 껑충 뜁니다. RF 도파관에서 플랜지 사이의 0.5 mm 오정렬은 VSWR을 1.2에서 1.8로 증가시켜 전송 전력의 15%를 낭비합니다. 전자빔 리소그래피(EBL)와 같은 고급 제작 도구는 특징 오류를 $\pm 2 nm$로 줄이지만, 시간당 \$500의 비용으로 정밀 응용 분야에 예약되어 있습니다.

“화학 기계적 연마(CMP)는 표면 거칠기를 10 nm에서 0.5 nm로 떨어뜨려 산란 손실을 80% 줄일 수 있습니다. 하지만 300 mm 웨이퍼를 1 $\mu m$ 과도하게 연마하면 다이의 5%가 망가집니다.”

포토리소그래피 정렬 오류 또한 치명적입니다. 도파관 층 사이의 100 nm 오버레이 불일치는 결합 인터페이스당 1 dB 삽입 손실을 유발합니다. $\pm 20 nm$ 정확도를 가진 자동 정렬 시스템(비용: 단위당 \$200k)을 사용하면 이 문제를 해결할 수 있지만, 더 저렴한 접촉 마스크 정렬기($\pm 1 \mu m$)는 3 $\mu m$보다 큰 특징에 충분합니다. 질화규소 도파관의 경우, $800^\circ C$에서 저압 화학 기상 증착(LPCVD)은 0.1 dB/cm 손실 필름을 생성하는 반면, $300^\circ C$에서 플라즈마 강화 CVD(PECVD)는 5% 더 높은 수소 함량으로 인해 1 dB/cm에 도달합니다.

에칭 화학은 측벽 품질을 극적으로 바꿉니다. 보쉬 프로세스($SF_6/C_4F_6$ 교대)는 50 nm 스캘럽을 생성하여 $-110^\circ C$에서 극저온 에칭의 0.05 dB/cm에 비해 0.3 dB/cm 손실을 추가합니다. 그러나 극저온 도구는 2배 더 많은 헬륨($50/시간$)을 소비하고 처리량을 40% 늦춥니다. 저예산 실험실의 경우, $O_2$ 플라즈마 디스컴을 사용한 최적화된 반응성 이온 에칭(RIE)은 측벽 잔해를 70% 줄여 손실을 0.8 dB/cm로 낮춥니다.

클린룸 프로토콜은 대부분이 깨닫는 것보다 더 중요합니다. 클래스 1000 룸($\le 1,000$ 입자/$ft^3$)은 클래스 100($\le 100/ft^3$)보다 20% 더 많은 결함을 유발하여 도파관 손실 분산을 $\pm 0.2 dB/cm$ 증가시킵니다. ISO 4 등급 HEPA 필터(\$50k 업그레이드)를 설치하는 것은 월 1,000개 이상의 칩을 생산할 때 효과가 있지만, 소규모 배치의 경우 아세톤/메탄올로 웨이퍼를 이중 세척하면 웨이퍼당 \$5 미만의 비용으로 오염을 60% 줄일 수 있습니다.

후속 제작 어닐링은 평범한 도파관을 구제할 수 있습니다. 실리콘 포토닉 칩을 1시간 동안 $1,000^\circ C$에서 아르곤으로 가열하면 산소 결함이 줄어들어 손실이 3 dB/cm에서 1.5 dB/cm로 낮아집니다. 고분자의 경우, 365 nm에서 30분 동안 UV 경화하면 잔류 단량체가 가교되어 5년 동안 $\pm 0.1 dB/cm$ 이내로 손실을 안정화합니다.

표면 거칠기 감소

표면 거칠기는 도파관 손실의 가장 큰 원인 중 하나입니다. 1 nm RMS 거칠기조차도 산란 손실을 0.02 dB/cm 증가시킬 수 있으며, 10 nm 거칠기는 실리콘 포토닉스에서 손실을 2 dB/cm까지 급증시킬 수 있습니다. RF 도파관에서 10 GHz의 0.5 $\mu m$ 거친 내부 벽은 0.05 dB/m 감쇠를 추가하지만, 이를 0.05 $\mu m$로 연마하면 손실이 60% 줄어듭니다. 광섬유의 경우, 0.2 nm 표면 평활도(고급 연마로 달성 가능)는 장거리 통신에 중요한 0.001 dB/km 미만의 손실을 유지합니다.

에칭 공정은 거칠기에 큰 역할을 합니다. $SF_6$ 플라즈마를 사용한 표준 반응성 이온 에칭(RIE)은 3-5 nm 측벽 거칠기를 남기는 반면, 심반응성 이온 에칭(DRIE)은 에칭/부동태화 주기의 교대로 인해 >20 nm 스캘럽을 생성할 수 있습니다. 극저온 에칭($-110^\circ C$)으로 전환하면 거칠기가 <1 nm로 줄어들지만, 공정 시간이 40% 증가하고 헬륨 냉각 비용이 시간당 \$30 증가합니다.

| 제작 방법 | RMS 거칠기 (nm) | 추가 손실 (dB/cm) | 비용 영향 |

|---|---|---|---|

| 표준 RIE ($SF_6$) | 3-5 | 0.1-0.3 | +$0/웨이퍼 |

| DRIE (보쉬 프로세스) | 10-20 | 0.5-1.5 | +$50/웨이퍼 |

| 극저온 에칭 | <1 | 0.01-0.05 | +$200/웨이퍼 |

| 습식 화학 에칭 | 2-4 | 0.05-0.2 | +$20/웨이퍼 |

후속 에칭 처리는 거친 표면을 복구할 수 있습니다. $1,100^\circ C$에서 30분 동안 수소 어닐링하면 실리콘 도파관이 5 nm에서 0.3 nm RMS로 평활해져 손실이 1 dB/cm에서 0.2 dB/cm로 줄어듭니다. 그러나 이는 에너지 비용으로 웨이퍼당 \$100를 추가하며 고분자와 같은 온도에 민감한 재료와는 호환되지 않습니다. 알루미늄 RF 도파관의 경우, 과염소산에서 전기 연마하면 거칠기가 500 nm에서 50 nm로 줄어들어 화학 비용으로 미터당 \$5에서 전도율이 25% 향상됩니다.

증착 기술 또한 평활도에 영향을 미칩니다. 플라즈마 강화 CVD(PECVD) 질화규소 필름은 2-4 nm 거칠기를 가지는 반면, 저압 CVD(LPCVD)는 더 느리고 더 제어된 성장으로 인해 <1 nm를 달성합니다. 장단점은? LPCVD는 $800^\circ C$($PECVD의 경우 $300^\circ C$와 비교)에서 실행되며 3배 더 오래 걸리므로 생산 비용이 웨이퍼당 \$150 증가합니다.

기계적 연마는 무식하지만 효과적인 솔루션입니다. 화학-기계적 평탄화(CMP)는 도파관 표면 거칠기를 10 nm에서 0.5 nm로 줄여 산란 손실을 80% 줄일 수 있습니다. 그러나 과도한 연마는 의도한 것보다 5% 더 많은 재료를 제거하여 $\pm 10\%$ 도파관 폭 변화의 위험을 초래합니다. 이는 광학 모드를 이동시키고 결합 손실을 0.5 dB 증가시키기에 충분합니다.

저예산 프로젝트의 경우, KOH 또는 TMAH에서 습식 화학 에칭은 웨이퍼당 \$10의 비용으로 2-4 nm 평활도를 제공하지만, $\pm 15\%$ 치수 허용 오차가 있습니다. 또는 제작 후 산소 플라즈마 세척은 유기 잔류물을 제거하여 공정 가스에서 웨이퍼당 \$2만으로 측벽 거칠기를 30% 줄입니다.

굽힘 손실 최소화

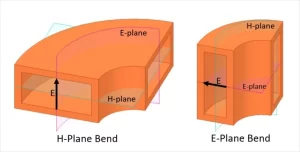

굽힘 손실은 도파관 성능을 망칠 수 있습니다. 실리콘 포토닉스에서 5 $\mu m$의 좁은 반경은 10 dB/cm를 누설하는 반면, 더 부드러운 50 $\mu m$ 굽힘은 손실을 0.05 dB/cm로 떨어뜨립니다. 광섬유에서 1550 nm의 2 mm 굽힘 반경은 0.1 dB/회전을 추가하지만, 1 mm로 좁히면 손실이 5 dB/회전으로 폭발합니다. RF 도파관도 유사한 문제를 겪습니다. 30° 마이터 굽힘이 있는 WR-90 도파관(10 GHz)은 0.2 dB를 손실하는 반면, 제대로 정합되지 않은 90° 엘보는 1.5 dB를 소모할 수 있습니다. 물리학은 간단합니다. 날카로운 굽힘은 빛이나 RF 파동이 산란되거나 누설되도록 강제하여 설계에 따라 전송 전력의 5-30%를 낭비합니다.

코어와 클래딩 사이의 굴절률 대비는 손실이 급증하기 전에 얼마나 좁게 굽힐 수 있는지 결정합니다. 표준 단일 모드 섬유($\Delta n=0.36\%$)는 30 mm 반경에서 누설을 시작하지만, 고 NA 섬유($\Delta n=2\%$)는 0.5 dB/회전 페널티만으로 5 mm 굽힘을 처리합니다. 통합 포토닉스에서 200 nm 산화물 클래딩($n=1.45$)을 가진 실리콘 도파관($n=3.5$)은 10 $\mu m$ 반경에서 3 dB/cm 손실을 겪는 반면, 동일한 클래딩을 가진 질화규소($n=2.0$)는 낮은 굴절률 대비 덕분에 이를 0.3 dB/cm로 줄입니다.

굽힘 전이 설계는 반경만큼 중요합니다. 포토닉 칩에서 갑작스러운 90° 회전은 1 dB를 손실하지만, 오일러 나선형 굽힘(점진적으로 증가하는 곡률)은 이를 0.2 dB로 줄입니다. 동일한 원리가 RF 도파관 모서리에도 적용됩니다. 5G 밀리미터파(28 GHz) 플렉스 PCB의 경우, 0.5 mm 반경을 가진 곡선 마이크로스트립 라인은 날카로운 직각 트레이스에 대한 1.2 dB에 비해 <0.3 dB 손실을 유지합니다. 문제는? 오일러 굽힘은 3배 더 많은 공간을 차지합니다. 이는 풋프린트와 성능 사이의 절충안입니다.

모드 변환기는 일시적으로 물리학을 속일 수 있습니다. 단열 테이퍼링된 도파관 섹션(300 $\mu m$ 길이)은 굽힘 전에 강력하게 가둠된 모드를 더 넓은 프로파일로 변환하여 10 $\mu m$ 굽힘 손실을 8 dB/cm에서 1 dB/cm로 줄입니다. 유사하게, 리튬 나이오베이트 도파관의 TE-to-TM 모드 회전기는 굽힘 섹션에서 편광 의존 손실을 50% 줄입니다. 이러한 트릭은 10-20% 제작 복잡성을 추가하지만, 밀집된 포토닉 회로에서 70% 전력을 절약합니다.

재료 선택은 숨겨진 역할을 합니다. 칼코게나이드 유리 도파관은 깨지기 전에 실리카보다 8배 더 좁은 굽힘을 견디는 반면, 유연한 고분자 도파관(SU-8, PDMS)은 <0.1 dB 손실로 1 mm 굽힘 반경에서 살아남습니다. 이는 착용형 광학에 이상적입니다. RF의 경우, 공기 채워진 구리 도파관은 모드 왜곡이 발생하기 전에 유전체 채워진 버전보다 15% 더 날카로운 굽힘을 처리합니다.

제조 공차는 굽힘 성능을 좌우합니다. 포토닉 와이어 굽힘에서 $\pm 50 nm$ 폭 오류는 손실 변동성을 $\pm 0.5 dB/cm$ 증가시킵니다. UV 리소그래피($\pm 50 nm$) 대신 전자빔 리소그래피($\pm 2 nm$ 정밀도)를 사용하면 이 페널티가 제거되지만, 5배 더 높은 비용이 발생합니다. 저예산 프로젝트의 경우, 제작 후 레이저 트리밍은 0.1 dB 정밀도로 굽힘 오류의 10%를 수정할 수 있으며, 처리에 칩당 \$3만 추가됩니다.